JETIR.ORG

# ISSN: 2349-5162 | ESTD Year : 2014 | Monthly Issue

# JOURNAL OF EMERGING TECHNOLOGIES AND INNOVATIVE RESEARCH (JETIR)

An International Scholarly Open Access, Peer-reviewed, Refereed Journal

# PERFORMANCE OPTIMIZATION OF HIGH LEVEL ARCHITECTURE ON OVERLOADED CDMA CROSSBAR SWITCH FOR NETWORK-ON-CHIP

P.SRIKANTH<sup>1</sup>,Dr.B.NAGESHWARRAO<sup>2</sup>,Dr.T.VAMSHI<sup>3</sup>

<sup>1</sup>M.TechStudent, Talla Padmavathi College of Engineering, Somidi, Kazipet, Telangana, 506003 <sup>2</sup>AssocProfessor, Talla Padmavathi college of Engineering, Somidi, Kazipet, Telangana, 506003 <sup>3</sup>Assoc Professor, TallaPadmavathi College of Engineering, Somidi, Kazipet, Telangana, 506003

<sup>1</sup>srikanthpalle6805@gmail.com, <sup>2</sup>nagesh.south@gmail.com, <sup>3</sup>vamshi22g@gmail.com

#### **Abstract**

The current system on-chips' execution is slowed down due to the high cost of on-chip couplers. On-chip crossbars have been proposed to use CDMA because of its settled idleness, reduced mediation overhead, and maximum transmission limit. By assigning an amount of N-chip length asymmetric rf chains to the getting-ready segments that share the same interface, CDMA makes it possible to share medium in the code space. Overtrouble CDMA interconnection (OCI) is developed in this research to increase the number of useable spreading codes in order to update the maximum cdma sort off on-chip (NoC) crossbars. Different regions, deferments, and power requirements are accounted for in serial communication OCI outline forms. On a Cpu Artix-7 AC701 Programmable logic pack, again the serial OCI load balancer outperforms the conventional CDMA backboard in terms of exchange speed by 100%, resource use by 31%, and power consumption by 45%, while the linear OCI crossbar outperforms the serial OCI goal line in terms of information communications by N times, all else being equal. Astronomical data centres (ADCs) have been completed, scanned and distinguished for 65 centres of OCI-based star NoC development. A promising breakthrough in the osi model of NoC switches is the OCI, according to the results of the evaluation

Keywords: CDMA, ADC, NoC, TDMA, OCI, PE

#### 1. Introduction,

The broad zone, implementation, and power consumption of contemporary system on-chips are all influenced significantly by on-chip trades of this sort (SoCs). Amdahl's law [1] shows that increasing the correspondence overhead taints the speedup realized by parallel figuring. Parallel and world-class preparation advancements necessitate the development of on-chip interconnects capable of unparalleled performance. Methodologies on-chips (NoCs) are by far the most flexible frame relay perspective that would be prepared to watch out for variety of application needs but rather meet the unmistakable execution requirements of generous workloads, along with determinant factor by strategies for flexible cooperation [3], improve the delivery by strategies for improved significantly different assortment [4], power diffusing by redoing the NoC to centred workflows [5], and fluidity

by run-time setup [6]. [2]. While on-chip segments (PEs) are treated framework centre points between connected by techniques for switches and switches, data are maintained as packs in NoCs. NoCs provide a flexible response for extremely large SoCs, but at the cost of considerable power consumption and resource consumption [7]. There are four layers: 1) program; 2) transport; 3) architecture and 4) core network in the NoC layer model [8]. The physical layer of the NoC relies heavily on the crossbar. When it comes to physical package exchange, a crossbar switch is a common correspondence medium that uses a different access technique than most. TDMA (time-division multiple access) and SDMA (space-division distinctive access) are two common resource sharing mechanisms supported by existing NoC crossbars. TDMA uses time-division multiple access to distribute the physical association across the interconnected PEs [9, 10]. A NoC switch's physical layer also includes buffering and limiting devices [7].

Another approach for sharing a medium, code-division multiple access (CDMA), also makes use of code space to enable simultaneous media access. Data from all transmitters is aggregated in a separate substance correspondence channel for each TX-RX coordinate in CDMA channels. Each TX-RX coordinate is assigned an unusual bipolar spreading code. A correlator decoder is required by the CDMA forager to properly decode the received data in symmetrical CDMA systems because of the zero cross-association between the symmetrical codes. Symmetrical Walsh-Hadamard symmetrical codes are used in CDMA structures that have been built up. For both tdm and NoC interconnect topologies, CDMA has been considered as a sharing mechanism for on-chip interconnect. Using CDMA for on-chip couplers has numerous advantages, including reduced power consumption, established correspondence inertness, and reduced structural diserseness [12]. With less wiring atmakur than an SDMA bridge and less attention expense than a TDMA switched, it provides an excellent combination of the two advantages. However, only the most fundamental aspects of CDMA advancement have been explored in the on-chip connection composition.

#### 2. Related work

In crossbar switches, adopting CDMA as either a medium access pattern improves the stability of the market & reduces overhead. For reducing the number of parallel business lines and goal (PTP) transports while maintaining a crucial separation from TDMA judges' overhead, Nickel faucet et al. [16] has developed an adjustable CDMAbased peripheral transport. Stick checks are reduced when several peripherals are connected to a single PE using this method since less line are utilized to transport data from the peripherals. Because peripherals typically operate at lower frequencies than ace PEs, the increase in trade torpidity caused by data spreading is tolerable. In [17] and [18], a master-slave transport wrapper was proposed, where the data are packed and disseminated using asymmetric CDMA codes to reduce the number of paralleled trade lines. Interconnection with other TDMA transports is not urged by the control signals. A TDMA divide trade transport has been distinguished from another CDMA transport use [11]. With an increasing number of passengers, CDMA transport outperforms split trade transport because it avoids the transport battle and covering delays that irritate TDMA transport's flexibility. [19] uses a shocked 2-bit CDMA transport as an info (I/O) configuration system that also shows a decrease in the vehicle fight over the Retransmission transport. The CT-Bus, which multiplexes data over time and code areas, has included both CDMA and TDMA [12]. As CDMA transport controllers broadcast simple spreading codes, the CT-Bus shows that CDMA's correspondence overhead is lower than TDMA's because the TDMA control must conduct watchfulness every clock cycle. The CT-Bus implementation outperforms its TDMA partner for diverse action because it combines the TDMA transporter flexibility well with CDMA channel congruence.

# 2.1. Classical CDMA Crossbar Switch

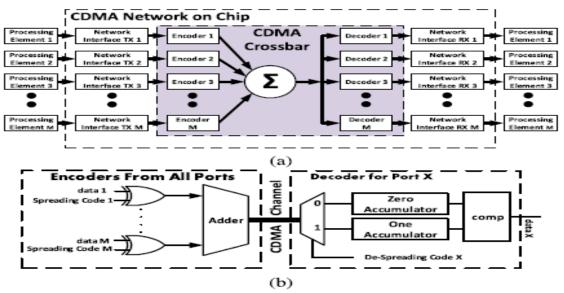

Fig. 1(a) shows a CDMA-based NoC switch's strange state planning. The data link layer of the changeover is determined by the CDMA switch, as seen in Fig. 1 by Nikolic and colleagues [16]. (b). XOR encoders, a lane snake, and aggregator-based decoders are used to make the transformation. To demonstrate that a single piece is spread over N time slots in the encoder, a Walsh spreading codes set is Multiplied with the transmitted bit and passed on sequentially. Rehashing crossbar exchanges and working clocks is thus related as ft=fc/N, where ft stands for crossbar exchange. When it comes to trademark and necessity differences, on chip interconnects aren't exactly the same as distant channels. To complete the OCI plot tests, key features that over CDMA will be proved from the perspective of the on-chip connection.

- 1) DSSS-CDMA uses a medium access mechanism known as overloaded CDMA for remote exchanges.

- 2) On-chip interconnects require basic correspondence, while distant over-stack CDMA's multidimensional

architecture limits its congruence with on-chip interconnect.

- 3) On-chip interconnects, such as FPGAs, can benefit greatly from baseband-coordinated CDMA, despite the fact that distant CDMA is frequently used in connection with other modification methods.

- 4) On-chip interconnects, such as clack, clouding and MAI, can be appropriately controlled using screw-up recognition verification and change frameworks because they are considered as optional effects in fundamental correspondence channels. As a result, the self-emphatic effects of this paper are not taken into consideration. Since the two previous hypotheses have been confirmed, the CDMA beneficiaries' complex thinking can be simplified to meet the on-chip connectivity requirements.

Fig. 1. (a) CDMA NoC router architecture. (b) Classical CDMA crossbar.

# 3. Literature survey

# **Exploiting emergence in on-chip interconnects.**

We advocate for inner (creating) structures on-chip to address the stunning inconveniences of present chip charting, such as method to centre mapping, vitality degradation, and support for programming engineer/equipment reflection (NoC). The architecture and data stream of these structures are constantly changing to allow up the overall efficiency or limit the structure's inertia through tactics for distributed use of smaller scale rules. New chart options such as Skip-interfaces, which update execution and reduce the relevance of multicenter framework utilisation are reviewed in this study. It is shown that our offered approach can be applied to many different development patterns, resulting in a 20% reduction in info ricochet check while maintaining energy and zone expenses. Furthermore, we demonstrate how emanant systems may benefit from on-chip processor to processor correspondences and show whether SoC and off-chip I/O performance can be enhanced for torpidity and the primary stack.

Author(s)- Simon J. Hollis graduated from college of Cambridge with a BA in programmed management in 2003 and a PhD in computer science in 2007. He is forthrightly a teacher in programmer working at the University of Bristol, Great Britain. To acknowledge his excellence as an educator, he received both the PGCHE and the Dewar Award for Excellence in Teaching in 2010. Altera Ltd. and Eton Corporation are two of his previous employers. When it comes to many-center scaling, energy efficiency, interconnects as well as parallel programming immaculate models, he is the man in charge of Bristol's many-center research path. In these areas, he has

distributed more than a dozen sidekick-examined papers. As of 20003, he is a member of the IEEE. After earning an MEng in Computer systems and programming delineation from the University of Sheffield in the United Kingdom in 2007, Chris Jackson went on to earn a PhD from the Agency of Computer Science at the University of Cape town, where he has been working since 2008. He has drafted and co - author papers on the outline and examination of Network-on-Chip. On-chip connections structures, planning calculations, software reenactment, specified advancement ages, and system topologies are all intertwined in his cadenced development research. He is a student member of the IEEE, a non-profit organization.

# 4. Proposed system

### 4.1 overloaded cdma interconnect

An M-port CDMA switch is available. The main difference between overburdened and developed CDMA switch seems to be that M > N 1 for the former due to channel overburdening. The transmit and receive NI modules are connected to each PE via two system interfaces (NIs). It is necessary to separate the parcel into bounces before storing it in the send NI only first yield during the transmission of a bundle from a PE (FIFO). M winning dances from the NI FIFOs are selected by the change referee at this moment to be relayed during the current exchange. To avoid collisions, they selected bounces that could all give an elite goal, and a champion from two conflicting flutters was selected by the switch's plan. Only one transmitter is given a routing protocol but is known to begin encoding in the used need plot, which is the established victor that swallows all need plans. Afterward, the switch allocates Lte codes to each transmission and reception NI. Zero CDMA codes are given out to NIs with void FIFOs or conflicting purposes so that they don't add MAI towards the CDMA channel aggregation. The encoder module's CDMA codes disseminate flutters from each NI a little time afterwards.

# 4.2 OCI Crossbar High-Level Architecture

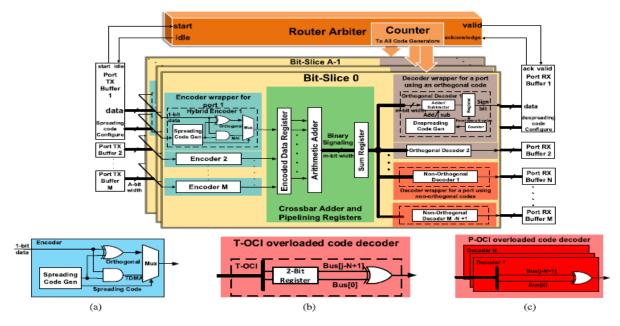

Expanding port numbers while keeping the framework's many-sided quality unaffected is a primary objective of this article, which uses easy encoding hardware and relies on the aggregating decoder with minor modifications. A few modifications to the existing CDMA crossbar are being implemented in order to achieve this goal. Figure 2 depicts the OCI crossbar in an atypical state of engineering for a single-piece link. A multi-bit CDMA switch uses the same kind of engineering. Using a math dual viper with M twofold information sources and an m-bit yield, spread knowledge from the transmits ports is included in the CDMA switch, which is shared by M TX-RX ports. Reference and cascaded models each include a viper that's been actualized.

Non-symmetrical spreading codes employ an AND entryway instead of asymmetrical distributing codes, which are XORed only with parallel information bit. if the sent information bit is "0," the encoder transmits a surge of zeros throughout the whole spreading cycle; if the transmitted bit bit is "1," the coder sends a non-symmetrical spreading code. This causes no MAI on the channel. Because the encoding is an AND entryway, the extra MAI dispersing code could either contribute one or zero MAI estimations per clock cycle. To encode OCI codes, a crossbar XOR encoder can't be used since it only supplies the spread code chips, therefore if the information bit either "0" or "1," an XOR entrance will MAI the crossbar. For both symmetry and non-symmetrical spreading, as shown in Fig. 2, a mixed encoder is constructed using an XOR doorway, an AND door, and just a multiplexing

unit. Two different decoder compositions are used for symmetry and non symmetric input respectively.

# 4.3 OCI Code Design

When it comes to CDMA connection over-burdening, the Walsh– Experience frequent spread code group has a built-in characteristic that facilitates it. It doesn't matter how much distributed information there is between any two back-to-back channels of information disseminated using the symmetric spread codes for in an odd of TX-RX sets M. When using the Walsh symmetry codes, it is possible to include additional information bits into sequential differences between both the N chips that make up the code's N 1 TX/RX sets. Using this trait, it is possible to include 100% non-symmetrical spread codes, which can double the capacity of the typical CDMA crossbar. OCI codes are outlined in this section, including the coding approach, numerical foundations, and translation details.

As shown in Fig. 2, an AND cascade encoder is used to encode data using non-symmetrical spreading codes (a). A single spreading chip added to the station total at a specific schedule vacancy in the distributing cycle causes the repeated entirety distinction to go wrong for a non-symmetrical encoder if material to transmit is one. The non-symmetrical codes mimic the TDMA flagging scheme by using a single "1" chip sent at a certain opening in the schedule. As described in this study, an innovative encoding/interpreting scheme enables the combination of CDMA and TDMA motions on the same common channel. As a result, the encoder developed is known as TDMA connection over there on CDMA (T-OCI). Two T-OCI codes of length N = 8 are shown in Fig. 3 as an example of an encoding/decoding instance. Walsh codes must be used with an odd of symmetrical codes in order to preserve their even contrast.

Non-symmetrical spreading codes are encoded using an AND entryway encoder, as shown in Fig. 2. (a). In this way, a single spreading chip is introduced to the channel aggregating at a certain schedule hole in the spreading cycle for a non-symmetrical encoder, causing the subsequent total contrast to diverge.

Fig2:OCI for NoCs: Analytical Evaluation

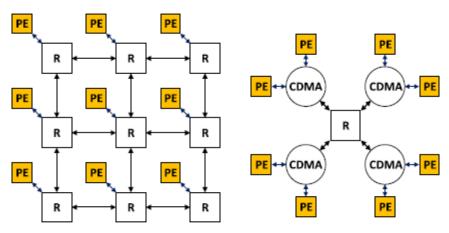

A 65-hub configuration is constructed using five OCI switches, each of the 13 PEs is connected to an OCI switches with N = 8, or the five OCI relays are joined by an SDMA focused switch. A 64-hub, 16-bit tango, and 8-ary 2-3D rectangular torus SDMA-based NoC developed by the CONNECT gear are contrasted with T-OCI-and P-OCI-based NoCs. The 65-hub 's currently star NoC and the SDMA-based torus NoC developed by CONNECT were both acknowledged and compared. Predominance is shown in terms of both territory and throughput for OCI-based NoCs.

Fig. 6. (a) CONNECT torus topology (b) versus the OCI star topology.

# 5. Results

Fig3.Entity diagram:

Fig4.RTL schematic:

f437

Fig5.Simulation results:

Name

Value

0 ns 200 ns 400 ns 600 ns 800 ns  $\mathbb{Z}_{Q}(31.0)$  011101010110011  $\mathbb{Z}_{Q}(31.0)$  011101010110011  $\mathbb{Z}_{Q}(31.0)$  0111010101010011  $\mathbb{Z}_{Q}(31.0)$  01110101010101011  $\mathbb{Z}_{Q}(31.0)$  011101010101011011  $\mathbb{Z}_{Q}(31.0)$  011101010101011011

### 6. Conclusion

Overloaded CDMA crossbars were introduced in this study as such physical layer enabler for NoC routers. CDMA is saturated with non - orthogonal codes to boost the channel capacity in overloaded CDMA. T-OCI and P-OCI, two crossbar architecture that make use of the overloaded CDMA principle, have been developed to boost the CDMA crossbar throughput by 100% and 2N 100%, respectively. It was possible to extend the numbers of router ports accessing the crossbar without changing the simple buffer decoder design of the typical CDMA crossbar using the Walsh disseminating code family. The nonorthogonal spreading code generation algorithms and the reference and pipelined designs for each crossbar variant are described. Artix-7 AC701 FPGA test kit was used to implement and test T/P-OCI crossbars. The OCI crossbars are compared to the traditional CDMA crossbar in terms of performance. The T-OCI crossbar has a dynamic power reduction of 45% while the P-OCI crossbar has an increase of 133%. When compared to a standard CDMA crossbar, the T-OCI crossbar uses 31% scarce staff, whilst P-OCI crossbar consumes 400% more.

## 7. References

- [1] K. Casanova et al., "The landscape of parallel computing research: A view from Berkeley," Dept. EECS, Univ. California, Berkeley, CA, USA, Tech. Rep. UCB/EECS-2006-183, 2006.

- [2] P.Bogdan, "Mathematical modeling and control of multiracial workloads for data-center-on-a-chip optimization," in Proc. 9th Int. Sump. Newt.-Chip, New York, NY, USA, 2015, pp. 21:1–21:8.

- [3] Z. Qian, P. Bogdan, G. Wei, C.-Y.Tsui, and R. Marculescu, "A traffic aware adaptive routing algorithm on a highly reconfigurable network-onchip architecture," in Proc. 8th IEEE/ACM/IFIP Int. Conf. Hard./Soft. Code sign, Syst. Synch., New York, NY, USA, Oct. 2012, pp. 161–170.

- [4] Y. Due and P. Bogdan, "User cooperation network coding approach for NoC performance improvement," in Proc. 9th Int. Sump. Newt.-Chip, New York, NY, USA, Sep. 2015, pp. 17:1–17:8.

- [5] T. Majumder, X. Li, P. Bogdan, and P. Pande, "NoC-enabled multicore architectures for stochastic analysis of biomolecular reactions," in Proc. Design, Auto. Test Eur. Conf. Exhibit. (DATE), San Jose, CA, USA, Mar. 2015, pp. 1102–1107.

- [6] S. J. Hollis, C. Jackson, P. Bogdan, and R. Marculescu, "Exploiting emergence in on-chip interconnects," IEEE Trans. Compute., vol. 63, no. 3, pp. 570–582, Mar. 2014.

- [7] S. Kumar et al., "A network on chip architecture and design methodology," in Proc. IEEE Compute. Soc.

- Annul. Sump. (VLSI), Apr. 2002, pp. 105–112.

- [8] T. Bjerregaard and S. Mahadevan, "A survey of research and practices of network-on-chip," ACM Compute. Surd., vol. 38, no. 1, 2006, Art. no. 1.

- [9] Y. Due, Z. Qian, G. Wei, P. Bogdan, C. Y. Tsui, and R. Marculescu, "An efficient network-on-chip (NoC) based multicore platform for hierarchical parallel genetic algorithms," in Proc. 8th IEEE/ACM Int. Sump. Newt.-Chip (NCOs), Sep. 2014, pp. 17–24.

- [10] D. Kim, K. Lee, S.-J. Lee, and H.-J. You, "A reconfigurable crossbar switch with adaptive bandwidth control for networks-on-chip," in Proc. IEEE Int. Sump. Circuits Syst. (ISCAS), May 2005, pp. 2369–2372.

- [11] R. H. Bell, C. Y. Kang, L. John, and E. E. Swartzlander, "CDMA as a multiprocessor interconnect strategy," in Proc. Conf. Rec. 35th Asilomar Conf. Signals, Syst. Compute., vol. 2. Nov. 2001, pp. 1246–1250.

- [12] B. C. C. Lai, P. Schaumont, and I. Verbauwhede, "CT-bus: A heterogeneous CDMA/TDMA bus for future SOC," in Proc. Conf. Rec. 35th Asilomar Conf. Signals, Syst. Compute., vol. 2. Nov. 2004, pp. 1868–1872.

- [13] S. A. Hosseini, O. Javidbakht, P. Pad, and F. Marvasti, "A review on synchronous CDMA systems: Optimum overloaded codes, channel capacity, and power control," EURASIP J. Wireless Commun. Newt., vol. 1, pp. 1–22, Dec. 2011.

- [14] K. E. Ahmed and M. M. Farag, "Overloaded CDMA bus topology for MPSoC interconnect," in Proc. Int. Conf. ReConFigurableCompute. FPGAs (ReConFig), Dec. 2014, pp. 1–7.

- [15] K. E. Ahmed and M. M. Farag, "Enhanced overloaded CDMA interconnect (OCI) bus architecture for onchip communication," in Proc. IEEE 23rd Annul. Sump. High-Perform. Interconnects (HOTI), Aug. 2015, pp. 78– 87.

- [16] T. Nikolic, G. Djordjevic, and M. Stojcev, "Simultaneous data transfers over peripheral bus using CDMA technique," in Proc. 26th Int. Conf. Microelectron. (MIEL), May 2008, pp. 437–440.

- [17] T. Nikolic, M. Stojcev, and G. Djordjevic, "CDMA bus-based onchip interconnect infrastructure," Microelectron. Rel., vol. 49, no. 4, pp. 448–459, Apr. 2009.

- [18] T. Nikoli'c, M. Stoj'cev, and Z. Stamenkovi'c, "Wrapper design for a CDMA bus in SOC," in Proc. IEEE 13th Int. Sump. Design Diagnostics Electron. Circuits Syst. (DDECS), Apr. 2010, pp. 243–248.